Controlling discrete LED luminosity strength or color-mixing

There are a number of issues surrounding the control of discrete LEDs on a FPGA development board.

- a straight GPIO on/off control can cause, when on, the LED luminosity to be a bright point of light that causes pain in the eyes

- additionally, a GPIO on/off can limit a 3-emitter RGB LED to having only 2^3 = 8 discrete states of color, including OFF

One solution is to make use of PWM signals instead of ON/OFF GPIO to control each emitter of the board’s LEDs. Here’s an example.

Note that the GPIO control will hold the voltage application to the LED emitter as a steady ON, which is a continuous flow of current into the emitter. The LED emitter will be held at its maximum brightness when turned on. Note also that the PWM control will hold the voltage application to the LED emitter as a partial duty cycle, preventing a maximum current flow to the emitter, and reducing the LED brightness to a controlled level. For a single emitter LED, this allows for a simple way by which to control the luminosity level of a basic LED.

One more technique to this is mixing the three emitters of a discrete RGB LED. I arrived at the idea by observing the source code of the shipping BIST program of the Digilent Inc. Zybo Z7 development board. The color LED can be mixed, similar to a color palette on a PC, by use of varying the PWM duty cycle of each of the three emitters of the LED.

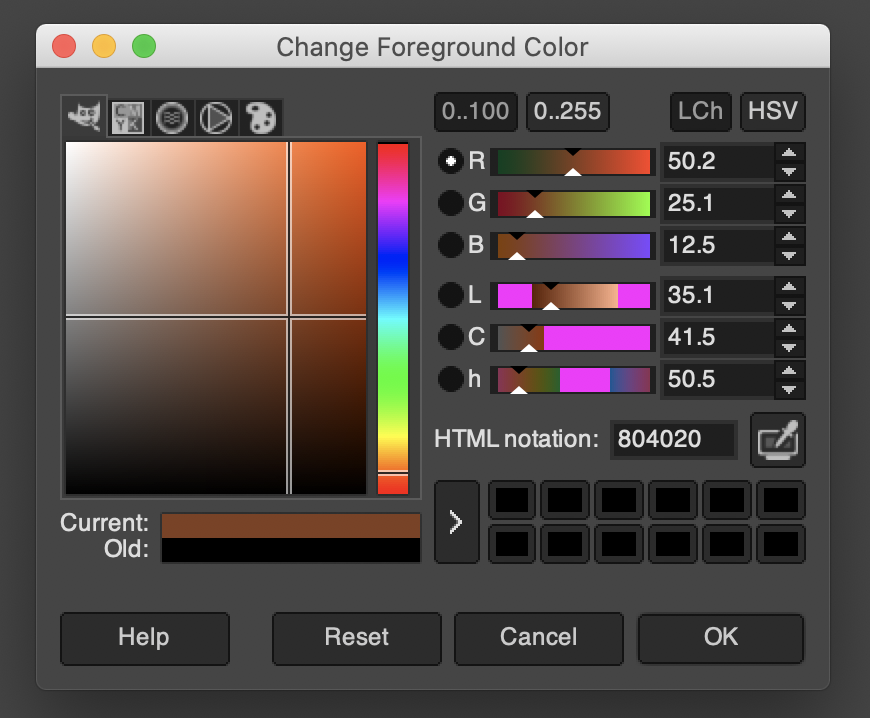

Here we have a color palette mixed on the PC that is a dark orange.

And to control the RGB color LED.

Note that a color palette of an PC imaging application will show dark color shades as the intensity of each color channel is lowered. That was not the result I encountered when mixing the RGB LEDs on the Arty A7. For the development board it was difficult to mix an Orange color; instead, the LED would range between different intensities of Yellow. I did accomplish an Orange color to indicate PAUSE BETWEEN OPERATIONS in the flash memory tester design. That project can be found here: fpga-serial-mem-tester-1 .

Feedback welcome on LinkedIn.