Flash Memory Tester on Arty A7

fpga-serial-mem-tester-1

FPGA Serial Mem Tester Version 1 by Timothy Stotts

FPGA Serial Mem Tester Version 1 project and source code

Description

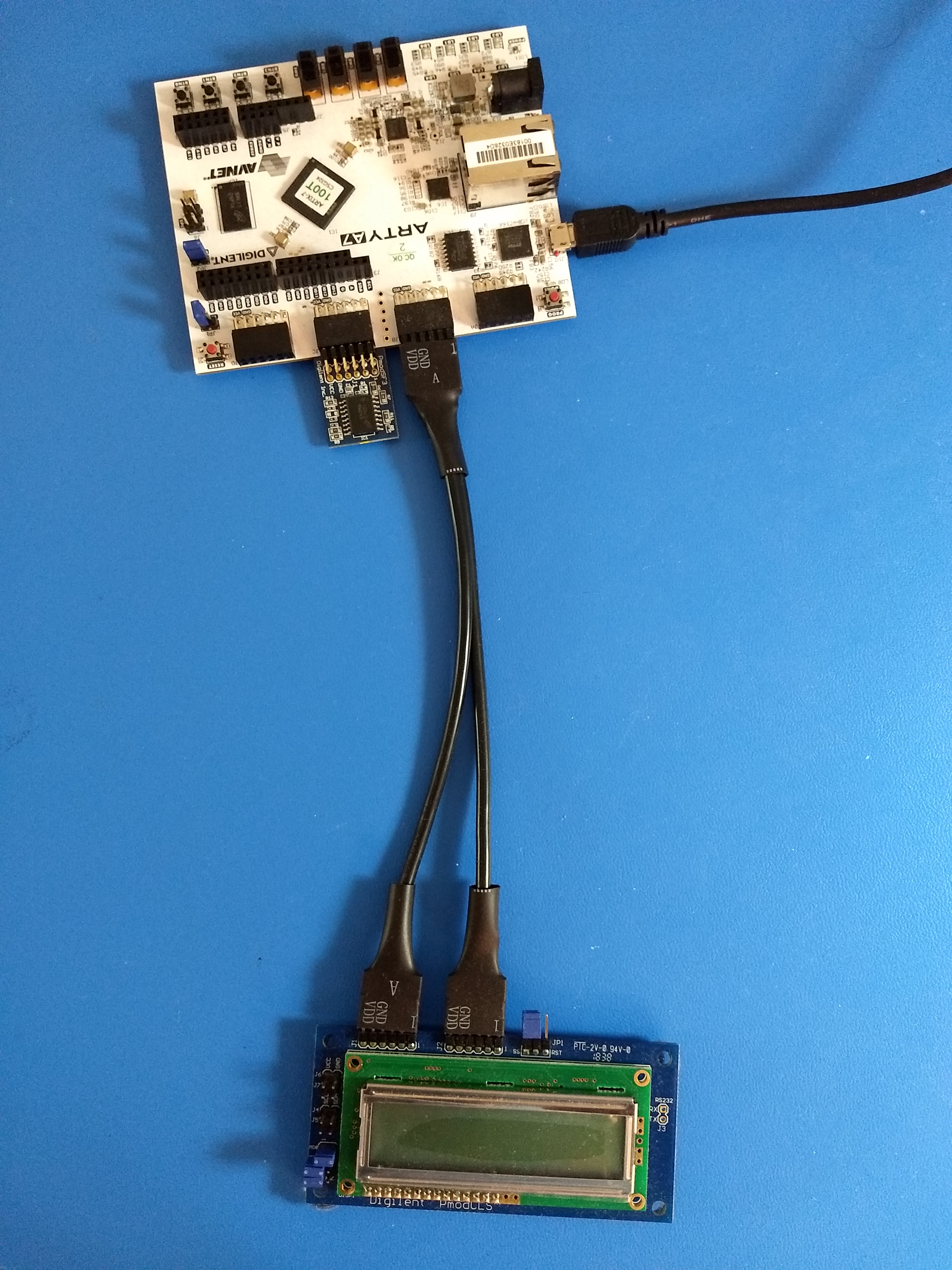

A small FPGA project of different implementations for testing byte-by-byte memory write/read bytes of a serial flash chip, N25Q. The design targets the Digilent Inc. Arty-A7-100T FPGA development board containing a Xilinx Artix-7 FPGA. Two peripherals are used: Digilent Inc. Pmod SF3, Digilent Inc. Pmod CLS. These are a SPI Flash peripheral, and a 16x2 character LCD peripheral.

The design is broken into two groupings.

The folder SF-Tester-Design-AXI contains a Xilinx Vivado IP Integrator plus Xilinx Vitis design. A microblaze soft CPU is instantiated to talk with board components, a SPI Flash peripheral, and a 16x2 character LCD peripheral. Sources to be incorporated into a Xilinx Vitis project contain a very small FreeRTOS program in C; drivers for the peripherals, a real-time task to operate the flash chip, two real-time tasks to display data, and a real-time task to color-mix RGB LEDs.

The folder SF-Tester-Design-VHDL contains a Xilinx Vivado project with sources containing only VHDL-2002 and VHDL-2008 modules. Plain HDL without a soft CPU or C code is authored to talk with board components, a N25Q SPI Flash 256Mbit, and a 16x2 character LCD peripheral.

The first grouping, SF-Tester-Design-AXI, has a limitation that only the first 128Mbits of the SPI flash can be addressed. The second grouping, SF-Tester-Design-VHDL, uses flash memory commands that address the full 256Mbits of the SPI flash.

Release pending

The Release A of this project is pending.

Naming conventions notice

The Pmod peripherals used in this project connect via a standard bus technology design called SPI. The use of MOSI/MISO terminology is considered obsolete. COPI/CIPO is now used. The MOSI signal on a controller can be replaced with the title ‘COPI’. Master and Slave terms are now Controller and Peripheral. Additional information can be found here. The choice to use COPI and CIPO instead of SDO and SDI for single-direction bus signals is simple. On a single peripheral bus with two data lines of fixed direction, the usage of the signal name “SDO” is dependent on whether the Controller or the Peripheral is the chip being discussed; whereas COPI gives the exact direction regardless of which chip is being discussed. The author of this website agrees with the open source community that the removal of offensive language from standard terminology in engineering is a priority.

Project homepage

FPGA Serial Flash Tester Version 1 project and source code

Project information document:

Serial Flash Sector Tester info

Diagrams design document:

Serial Flash Design Diagrams info

Target device assembly: Arty-A7-100T with Pmod SF3, and Pmod CLS on extension cable